作者:團子

審核專家:彭練矛,北京大學信息學院“博雅”特聘教授、納米器件物理與化學教育部重點實驗室主任

如今,人們的生活已經離不開智能手機。去年發布的iphoneXS手機容量最大可配置為512GB,而十年前8GB就已經能稱得上手機存儲的頂級配置了。短短十年,手機存儲幾十倍的增長正是集成電路高速發展的產物。此外,手機運行速度的加快、電腦尺寸的減小、存儲容量和主頻的增加等均與集成電路的發展息息相關。

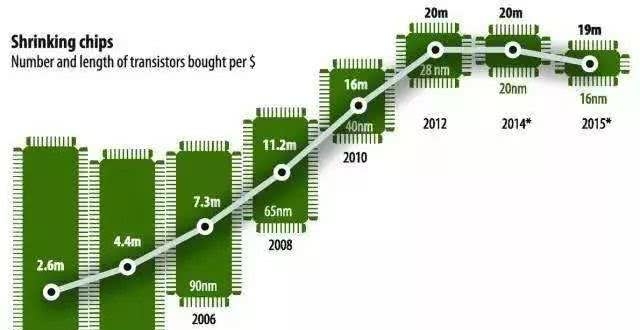

集成電路的最小功能部門為晶體管,配合一些被動元器件(如:電阻)可實現不同的功能。衡量集成電路的重要指標之一為集成度————部門面積的芯片上可容納的晶體管數量。

摩爾定律說,集成電路中晶體管的數量每兩年增長一倍。這條定律準確地預測了半導體行業的高速發展。在摩爾定律的指導下,過去的半個世紀裡,矽基集成電路的製造工藝一直穩步向前演進,半導體產業在歷經了上世紀六十年代的IC(集成電路)時代,八十年代的VLSI(超大集成電路)時代,發展到當下的Gb、Tb時代。而在未來較長的一段時間內,矽基集成電路依舊是半導體技術的主流。

近二十年來,晶體管的技術節點不斷縮小:130 nm、90 nm、 65 nm、 45 nm、 32 nm、 22 nm,14 nm,7 nm(當下最先進的製程),5/3 nm(研發中)。隨著技術節點的縮小,矽基芯片的集成度越來越高(即部門面積的晶體管數量的增加),隨之而來的是容量更大的存儲以及更快的計算速度。然而,不容忽視的一點是,高集成度帶來的功耗問題會影響芯片的工作可靠性以及晶體管的性能。因而,集成電路產業的主要目標已經由最初的提升性能和集成度轉變為降低功耗。

減小晶體管功耗最有效的方法是降低工作電壓(VDD)和提高晶體管開關態轉換速率。目前所使用的傳統矽基互補金屬氧化物半導體集成電路(14/10 nm技術節點)的VDD和SS值的極限值分別為0.64V和60mV/DEC(毫伏/量級電壓與開關轉換速率已達到了極限。新型微電子器件中能滿足小工作壓電和低亞閾值擺幅的有隧穿場效應晶體管、碰撞電離場效應晶體管和負電容場效應晶體管等。但這些晶體管有著速度低、穩定性差等重要缺陷。

在國家重點研發計劃“納米科技”重點專項的支持下,北京大學信息科學技術學院物理電子學研究所、納米器件物理與化學教育部重點實驗室張志勇教授、彭練矛教授課題組提出一種新型超低功耗的場效應晶體管——狄拉克源場效應晶體管(DS-FET)。

這種新型晶體管通過三個部分以下三個方面的調控調製溝道電學特性提高了性能:把晶體管比作一個電路,那麽摻雜石墨烯就是“電源”摻雜石墨烯為冷電子源,碳納米管即為“導線”為有源溝道,高效率頂柵結構而電路的開關在此種新型結構中效率也更高。多批器件測試結果顯示狄拉克晶體管的性能突破了傳統晶體管的極限值。並且當狄拉克晶體管的尺寸進一步縮小時,性能依舊穩定。且開態電流高於10微安,可與目前報導的性能最好的p型碳納米管場效應管相媲美。DS-FET不僅滿足超低功耗的要求還具有良好的可縮減性,完全達到了國際半導體發展路線圖的標準,極有希望成為將來亞0.5V集成電路的基礎元件。

狄拉克源晶體管的提出突破了傳統互補金屬氧化物半導體的亞閾值擺幅極限值60mV/DEC,在溝道縮短的情況下,性能依舊可觀。用作“導線”的材料除碳納米管外,石墨烯狄拉克源也可與還有多種其它半導體溝道材料選擇(如:尺寸在半導體納米級別的線狀結構、二維半導體材料或者傳統半導體材料等)相結合,這種靈活性與可兼容性為研發低功耗高性能晶體管提供了多種可能性,也為3nm以後技術節點的集成電路技術提供多種解決方案。

超低功耗集成電路晶體管介紹:

排版:凝音

題圖來源:Pixabay

歡迎個人轉發到朋友圈