傳統的計算機將數據儲存在記憶體中,然後傳送到處理器運算。這種來回“搬運”數據的活動耗費能源和時間,被認為是馮•諾依曼計算架構的核心瓶頸。

而人類的大腦卻並非如此,而是直接在記憶體裡計算。被認為具有“存算一體”潛力的憶阻器,因而成為類腦計算領域的熱門器件。

近日,清華大學微電子所、未來芯片技術高精尖創新中心錢鶴、吳華強團隊與合作者在頂尖學術期刊、英國《自然》雜誌(Nature)在線發表論文,報導了基於憶阻器陣列芯片卷積網絡的完整硬體實現。

該存算一體系統在處理卷積神經網絡(CNN)時能效比前沿的圖形處理器芯片(GPU)高兩個數量級,可以說在一定程度上突破了“馮諾依曼瓶頸”的限制:大幅提升算力的同時,實現了更小的功耗和更低的硬體成本。

什麽是憶阻器?

憶阻器,全稱記憶電阻器(Memristor),是繼電阻、電容、電感之後的第四種電路基本元件,表示磁通與電荷之間的關係,最早由加州大學伯克利分校教授蔡少棠在1971年預言存在,惠普公司在2008年研製成功。

簡單來說,這種組件的的電阻會隨著通過的電流量而改變,而且就算電流停止了,它的電阻仍然會停留在之前的值,直到接受到反向的電流它才會被推回去,等於說能“記住”之前的電流量。

這種奇妙的效果,其實和神經元突觸有相仿之處。再加上憶阻器還具有尺寸小、操作功耗低、可大規模集成(三維集成)等優點,難怪計算機科學家們在憶阻器身上看到了存算一體、低能耗類腦計算的前景。

人工神經網絡近年來大放異彩,如果用憶阻器連接成陣列,作為人工神經網絡的硬體,會有什麽效果?

憶阻器陣列

儘管國內外許多企業、研究機構給予關注,但據清華大學新聞頁面報導,當前國際上的憶阻器研究還停留在簡單網絡結構的驗證,或者基於少量器件數據進行的仿真。基於憶阻器陣列的完整硬體實現仍然有很多挑戰。

比如,器件方面,需要製備高一致、可靠的陣列;系統方面,憶阻器因工作原理而存在固有缺陷(如器件間波動,器件電導卡滯,電導狀態漂移等),會導致計算準確率降低;架構方面,憶阻器陣列實現卷積功能需要以串行滑動的方式連續采樣、計算多個輸入塊,無法匹配全連接結構的計算效率。

通過近年來積累的一些成果,錢鶴、吳華強團隊逐漸優化材料和器件結構,製備出了高性能的憶阻器陣列。

2017年5月,該課題組就曾在《自然通訊》報告稱,首次實現了基於1024個氧化物憶阻器陣列的類腦計算,將氧化物憶阻器的集成規模提高了一個數量級。這使芯片更加高效地完成人臉識別計算任務,將能耗降低到原來的千分之一以下。

憶阻器神經網絡

這次,錢、吳團隊集成了8個包括2048個憶阻器的陣列,以提高並行計算的效率。

在此基礎上,他們構建了一個五層的卷積神經網絡進行圖像識別,獲得了96%以上的高精度,結果顯示,基於憶阻器的卷積神經網絡比目前最先進的GPU的能效要高出兩個數量級。

這樣的提升是如何實現的?原來,為解決器件固有缺陷造成的系統識別準確率下降問題,他們提出了一種新型的混合訓練算法,僅需用較少的圖像樣本訓練神經網絡,並微調了最後一層網絡的部分權重。

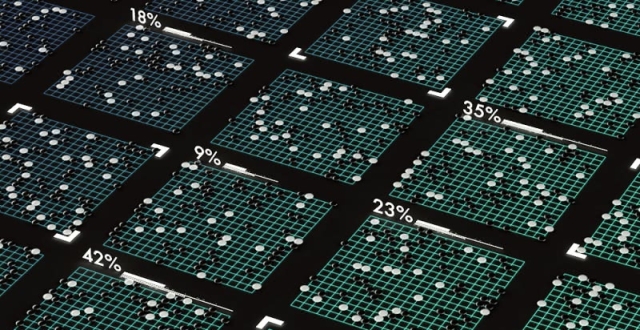

與此同時,他們提出了空間並行的機制,將相同卷積核編程到多組憶阻器陣列中,各組憶阻器陣列可並行處理不同的卷積輸入塊,提高並行度來加速卷積計算。

多個憶阻器陣列並行處理

隨著摩爾定律放緩,計算界翹首以待新的架構突破馮諾依曼瓶頸,適應越來越複雜的AI問題。基於憶阻器的存算一體系統在這場角逐中穩步前進。