摘要:近年來,人工智能(AI)產業發展十分迅速,湧現出了一大批的AI算法初創公司,與此同時谷歌、BAT等互聯網公司也紛紛殺入,但是隨著AI技術的逐步成熟,這個領域的競爭變得越來越激烈。

AI算法芯片化已是大勢所趨

近年來,人工智能(AI)產業發展十分迅速,湧現出了一大批的AI算法初創公司,與此同時谷歌、BAT等互聯網公司也紛紛殺入,但是隨著AI技術的逐步成熟,這個領域的競爭變得越來越激烈。

特別是在谷歌、百度等廠商將很多AI算法及工具開源之後,開發AI算法及應用的門檻開始大幅降低,與此同時很多AI算法廠商還紛紛將一些基礎的AI算法能力免費向開發者提供,比如百度將其語音AI能力免費開放,虹軟也將其基礎的視覺AI能力免費對外開放。這些都加劇了AI算法市場的競爭。

為了進一步提升自身的競爭力,越來越多的AI算法廠商開始紛紛進入半導體領域,不再選擇第三方的芯片作為載體,而是將“算法芯片化”,打造更為適合自己需求的,更具能效的,具有自主IP(知識產權)的專用型AI芯片,用以替代第三方的芯片。

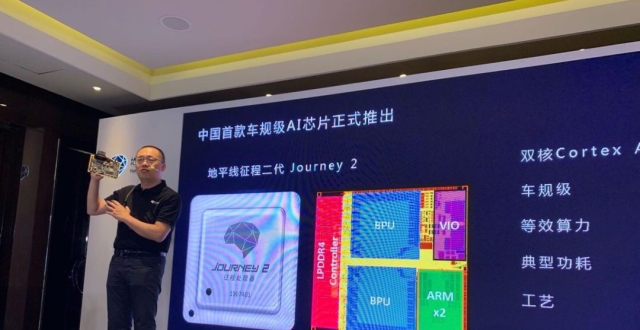

以國外廠商為例,Google很早就推出了自研的TPU;2017年,Intel以150多億美金收購了ADAS/自動駕駛AI芯片及解決方案廠商Mobileye,此外還收購了AI芯片公司Movidius;2018年,亞馬遜也曝光了自己的雲端AI芯片;不久前,特斯拉也推出了自己的自動駕駛AI芯片。

在國內市場也同樣如此,在過去的一年,我們可以看到,百度發布了自己的雲端AI芯片“昆侖”,雲知聲、Rokid、雲天勵飛等AI算法廠商都推出了基於自己算法定製的AI芯片。

顯然,對於AI算法廠商來說,自己來做AI芯片或模組,一方面可以脫離單純的AI算法授權的商業模式,脫離AI算法領域的激烈競爭,通過向產業鏈上下遊延伸,拉高競爭壁壘,同時可以提升自身的核心競爭力,推動生態建設,加速AI算法的產品化落地。

但是,對於大多數的AI算法廠商來說,由於缺乏半導體芯片的研發人才積累、技術積累和經驗積累,這也使得他們在將AI算法芯片化的過程中會遇到非常多的難題和挑戰。

針對這這一趨勢,全球知名的EDA工具及IP廠商新思科技(Synopsys)早前就推出了一套能夠實現專用指令集處理器(ASIP)開發流程自動化的工具——ASIP Designer,可以助力AI算法廠商快速高效的實現“算法芯片化”。

什麽是ASIP?

ASIP即“專用指令集處理器(內核)”,是針對特定應用場景的功能需求而設計的一類“指令集處理器”。與之相對的是,比如Arm的Cortex CPU內核則是屬於“通用型指令集處理器”。相對於“通用型指令集處理器”,ASIP在特定應用場景下可以獲得更為出色的性能、面積、功耗和成本等競爭優勢。

這裡需要區別的是,ASIP並不等於專用型處理器ASIC,我們通常所說的ASIC芯片是一個完整的芯片,其不僅包括針對特定算法設計或優化的內核,還包括了外圍的電路、接口等等。

ASIP有何優勢?

對於算法廠商來說,雖然市場上有很多現成的處理器內核可選,但為了覆蓋更多的用戶和市場,這些處理器內核往往都是偏向“大而全”,性能、面積、功耗也一定不是最優的。並且,這些內核都是固定的,難以進行修改的,更不能根據自己的應用需求去優化。

針對客戶的特定需求來說,買來的處理器內核可能只有部分指令用得上,有很多的指令是用不上的,這就造成了浪費。比如,算法廠商需要設計一個處理器來跑自己的20條指令,如果要用Arm內核來做,可能其內部很多指令用不上,同時還需要搞定Arm內核裡面的初始化和驅動,這就需要增加很多的指令,還會遇到面積、功耗、啟動時間等一大堆的問題。

相對而言,由於算法廠商對於自己的算法非常熟悉,如果採用自定義的處理器架構和指令集,那麽就可以實現極簡化的按需設計,並且可以通過不斷的修改和優化自己的架構,最終獲得比市場上可以買到的處理器內核更好的效果,實現高性能、低功耗、面積更小、成本更低等優勢。

新思科技相關人士表示,“從自動駕駛汽車到醫療器械,從智能移動網絡到空間應用,從安全到虛擬現實,幾乎每個片上系統都需要或已經使用ASIP。ASIP能夠滿足專業處理要求,現成的商用處理器IP無法滿足功率、性能、面積要求,固定功能硬體缺乏所需的可編程性。”

ASIP Designer能做什麽?

雖然ASIP有很多的優勢,但是ASIP的研發並不是一個簡單的工作,其工作量非常的大,不僅需要基於特定算法定義一套處理器模型架構,還要進行架構優化和軟體開發以及驗證ASIP設計,除此之外,還必須考慮開發用於對所得設計進行編程的軟體開發工具鏈需要完成的工作。

新思科技推出的ASIP Designer則是一套針對ASIP的開發流程自動化工具。其不僅能最大限度地減少開發專用處理器和相關編程工具所需的工程時間和工作量,而且還能加快理解候選設計的性能和效率(即設計探索)。

下面簡單解釋下ASIP Designer這套工具的作用:

比如一家AI算法廠商,希望開發出一個最為適合自己AI算法的處理器內核架構(完全自主設計,而不是基於Arm CPU內核架構或者其他的CPU/GPU/DSP內核架構),那麽這家AI算法廠商只需要自己定義一個架構,用nML語言就把它寫出來,通過ASIP Designer就可以自動生成一套SDK,包含優化的C/C 語言編譯器、匯編器/反匯編器、鏈接器、周期精確以及指令精確的指令集仿真器和圖形化調試器(適用於指令集仿真和片上調試)。這就形成了一個完整的最小化的嵌入式處理器內核模型及開發環境。

然後,算法廠商可以將自己的算法放到這個已經生產的嵌入式處理器內核模型及開發環境當中去運行,通過調試器和分析器來檢測出來的結果對不對、效率高不高,進而發現一開始的”用戶定義的架構“哪些地方有問題,哪些地方需要迭代修改。

由於ASIP Designer的所有編譯器優化都以通用方式實現,編譯器還可以自動可重定向。得益於編譯器的即時可用性,使得用戶可以通過ASIP Designer實現快速的架構迭代,進而使編譯結果能夠在下一個迭代步驟中推動架構的進一步優化。另外對於算法廠商本身的算法需要快速迭代的需求,ASIP Designer也可使得整個ASIP的設計能夠及時的進行相應的快速迭代。

據介紹,使用ASIP Designer完成一次完整的架構迭代可能只需要10分鐘。

如果採用的是現成的固定的處理器內核,那麽要完成一次算法的迭代需要修改非常多的東西,而且需要真正的仿真以後才能把這個算法跑起來。跑出來以後再看結果,再根據結果去修改,顯然這個迭代過程非常的複雜。

而當ASIP整個軟體代碼迭代完成之後,接下來就可以往硬體方面做了。

開發人員可以使用ASIP Designer的RTL生成工具將設計好的nML模型轉換為完全可綜合的Verilog或VHDL。因為nML可以對處理器進行周期和位精確描述,所以設計人員可以完全控制硬體。

不但如此,ASIP Designer還可以無縫對接新思科技的SoC的實現和驗證工具。比如,開發人員可以使用新思科技的RTL仿真器VCS進行進一步的模擬設計,然後進行驗證:驗證處理器模型(nML),確保指定的處理器模型實現所期望的行為;驗證RTL模型,確保生成的RTL模型正確實現nML。

如果發現nML問題,則可以很容易返回到nML描述,並對模型執行必要硬體和/或軟體修改以解決問題,例如超出功耗和/或面積預算。由於nML中的單一來源條目,SDK和RTL將始終保持同步。

開發人員還可以進一步的進行模擬設計,然後使用Design Compiler生成門級描述,門級描述可用於準確評估電路的功率要求和面積,甚至可以使用新思科技IC Compiler等工具進入布局和布線過程,以探索路由擁塞的風險。這種“環路綜合”方法可確保做出合理決策,並避免在設計過程的後期出現意外。

總結來說,ASIP Designer功能強大,同時可結合新思科技其他豐富的配套的EDA工具,在兼容性和內部協同性上更為出色,極大簡化了ASIP的設計流程,縮短了設計周期。如果是採用多個未全面整合的工具,那麽就意味著需要在工具間進行某一設計版本移植,而這是引發錯誤的一個主要原因。而要解決發現的問題,通常需要與兩個或兩個以上的不同的工具供應商溝通獲得技術支持,因此找出錯誤也將耗費大量的時間。

ASIP Designer明顯降低了就新設計項目採用ASIP所面臨的障礙。無需聘請仿真器、調試器或編譯器專家就可以獲得專業的技術支持,可以幫助設計團隊提高生產力和縮短上市時間。借助ASIP Designer,設計團隊可以:用ASIP替換固定功能硬體實現,進而避免設計和驗證複雜且不靈活的狀態;設計其自己專為特定算法量身定製的專用DSP,如圖像處理、基帶處理和音頻處理;為高價值和差異化設計區塊(如AI、第1層通信、矩陣運算)創建針對特定域的靈活加速器。

小結:

顯然,對於這些AI算法廠商來說,採用ASIP Designer完全可以設計出最為適合自身特定AI算法的具有自主知識產權的處理器內核,且可以加速算法IP化芯片化的迭代速度,降低流片失敗風險。

正所謂好馬配好鞍,要想真正把ASIP Designer這個工具用好,也有著一定的門檻。

新思科技內部技術人員表示,”只有開發團隊清晰明白自己需要的是一個什麽樣的硬體邏輯,才能夠把自身算法發揮到最佳“。特別是在“用戶定義架構”這個部分,非常考驗AI算法廠商在軟硬體結構定義的能力,需要一個非常有經驗的,對於軟硬體都非常精通的開發團隊,才能夠把ASIP Designer用好。

而據了解,目前一些海內外大客戶已經開始引入ASIP Designer,用於新的芯片的研發。國內外不少AI廠商、RISC-V芯片廠商也對ASIP Designer表現出了極大的興趣。

編輯:芯智訊-浪客劍